X

X

R

R

P

P

7

7

7

7

0

0

8

8

a

a

n

n

d

d

X

X

R

R

P

P

7

7

7

7

4

4

0

0

Q

Q

u

u

a

a

d

d

C

C

h

h

a

a

n

n

n

n

e

e

l

l

D

D

i

i

g

g

i

i

t

t

a

a

l

l

P

P

W

W

M

M

S

S

t

t

e

e

p

p

D

D

o

o

w

w

n

n

C

C

o

o

n

n

t

t

r

r

o

o

l

l

l

l

e

e

r

r

s

s

?2012 Exar Corporation

6/28

Rev. 1.2.2

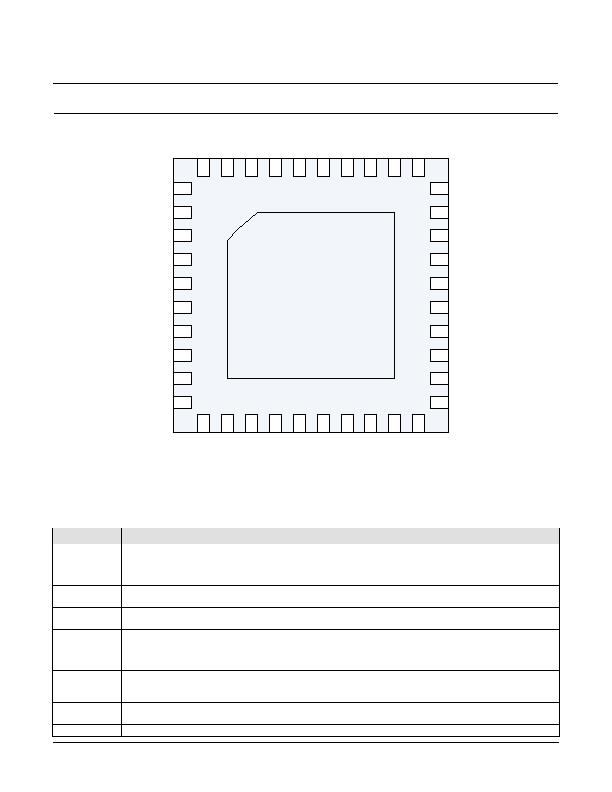

PIN ASSIGNMENT

30

29

28

27

26

25

24

23

21

22

10

1

2

3

4

5

6

7

8

9

AVDD

DVDD

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4_SDA

GPIO5_SCL

ENABLE

GL2

LX2

GH2

BST2

VCCD

BST4

GH4

LX4

GL4

PGND4

DGND

Exposed Pad: AGND

XRP7708

XRP7740

TQFN

6mm X 6mm

Fig. 3: XRP7708/40 Pin Assignment

PIN DESCRIPTION

Name

Pin Number

Description

VIN1

39

Power source for the internal linear regulators to generate VCCA, VDD and the Standby

LDO (LDOOUT). Place a decoupling capacitor close to the controller IC. Also used in

UVLO1 fault generation if VIN1 falls below the user programmed limit, all channels are

shut down. The VIN1 pin needs to be tied to VIN2 on the board with a short trace.

VIN2

38

If the Vin2 pin voltage falls below the user programmed UVLO VIN2 level all channels are

shut down. The VIN2 pin needs to be tied to VIN1 on the board with a short trace.

VCCA

37

Output of the internal 5V LDO. This voltage is internally used to power analog blocks. This

pin should be bypassed with a minimum of 4.7uF to AGND

VCCD

26

Gate Drive input voltage. This is not an output voltage. This pin can be connected to

VCCA to provide power for the Gate Drive. VCCD should be connected to VCCA with the

shortest possible trace and decouple with a minimum 1礔 capacitor. Alternatively, VCCD

could be connected to an external supply (not greater than 5V).

PGND1- PGND4

36,31,16,21

GL return connection. Ground connection for the low side gate driver. Connect at low side

FET source. Connecting to the ground plane at the chip will inject noise into the local

ground resulting in potential I

2

C communications problems and PWM jitter.

AVDD

1

Output of the internal 1.8V LDO. A decoupling capacitor should be placed between AVDD

and AGND close to the chip (with short traces).

DVDD

2

Input for powering the internal digital logic. This pin should be connected to AVDD.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ZDS1009TA

IC CURRENT MIRROR SOT223-8

ZXCT1008FTA

IC CURRENT MONITOR 1% SOT23-3

ZXCT1009T8TA

IC CURRENT MONITOR 1% SM8

ZXCT1010E5TA

IC CURRENT MONITOR 1% SOT-23-5

ZXCT1011E5TA

IC CURRENT MONITOR 1% SOT23-5

ZXCT1012DAATA

IC CURRENT MONITOR 2.5% 5TDFN

ZXCT1020E5TA

IC CURRENT MONITOR 1% SOT23-5

ZXCT1021E5TA

IC CURRENT MONITOR 1% SOT23-5

相关代理商/技术参数

XRP77XXEVB-XCM

功能描述:EVAL BOARD W/USB-I2C FOR XRP7704 RoHS:是 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969

XRP77XXEVB-XPM

功能描述:电源管理IC开发工具 XRP77XXEVB-XPM RoHS:否 制造商:Maxim Integrated 产品:Evaluation Kits 类型:Battery Management 工具用于评估:MAX17710GB 输入电压: 输出电压:1.8 V

XRP9710EVB

制造商:Exar Corporation 功能描述:Evaluation Board for the XRP9710 Series Dual 6 A Programmable Power Module 制造商:Exar Corporation 功能描述:XRP9710 eval

XRP9710EVB-DEMO-1

功能描述:XRP9710 - DC/DC, Step Down 2, Non-Isolated Outputs Evaluation Board 制造商:exar corporation 系列:- 零件状态:有效 主要用途:DC/DC,步降 输出和类型:2,非隔离 功率 - 输出:- 电压 - 输出:1.8V,2.5V 电流 - 输出:6A,6A 电压 - 输入:5.5 V ~ 22 V 稳压器拓扑:降压 频率 - 开关:- 板类型:完全填充 所含物品:板 使用的 IC/零件:XRP9710 标准包装:1

XRP9710EY-F

制造商:Exar Corporation 功能描述:Dual 6Amp Programmable Power Module

XRP9711EVB-DEMO-1

功能描述:XRP9711 - DC/DC, Step Down 4, Non-Isolated Outputs Evaluation Board 制造商:exar corporation 系列:- 零件状态:有效 主要用途:DC/DC,步降 输出和类型:4,非隔离 功率 - 输出:- 电压 - 输出:1.2V,1.5V,1.8V,2.5V 电流 - 输出:10A,10A,6A,6A 电压 - 输入:5.5 V ~ 22 V 稳压器拓扑:降压 频率 - 开关:- 板类型:完全填充 所含物品:板 使用的 IC/零件:XRP9711 标准包装:1

XRP9711EY-F

功能描述:Linear And Switching Voltage Regulator IC 3 Output Step-Down (Buck) Synchronous (2), Linear (LDO) (1) 126kHz ~ 1.23MHz 45-BLGA 制造商:exar corporation 系列:- 包装:托盘 零件状态:有效 拓扑:降压(降压)同步(2),线性(LDO)(1) 功能:任何功能 输出数:3 频率 - 开关:126kHz ~ 1.23MHz 电压/电流 - 输出 1:0.6 V ~ 5.5 V,6A 电压/电流 - 输出 2:0.6 V ~ 5.5 V,6A 电压/电流 - 输出 3:5V,135mA 带 LED 驱动器:无 带监控器:无 带定序器:是 电压 - 电源:4.75 V ~ 22 V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:45-BLGA 供应商器件封装:45-LGA(12x12) 标准包装:260

XRPB-06F1AX

制造商:BEL 制造商全称:Bel Fuse Inc. 功能描述:NON-ISOLATED DC/DC CONVERTERS 3.0 V-5.5 V Input 0.75 V-3.63 V/6 A Output